Semestre: 2

Unité d’enseignement: UEF 1.2.1

Matière 1: Processeurs numériques du signal (DSP)

Objectifs de l’enseignement:

Connaître l'architecture interne d'un DSP et la plateforme matérielle intégrant ce DSP ainsi que l'environnement de développement sur une plateforme à base de DSP. A l'issue de cette matière, l'étudiant doit maîtriser le flot de conception et doit être également en mesure de faire une adéquation algorithme-architecture pour l'implémentation d'algorithmes sur une plateforme à base de processeurs DSP.

Connaissances préalables recommandées :

Systèmes à microprocesseurs. Traitement numérique avancé du signal. Programmation en langage assembleur et C.

Chapitre 1 : Généralités sur les processeurs DSP (1 semaine)

- Définitions, présentation des différentes familles de DSP, classification des DSP, domaines d’applications des DSP, principaux algorithmes traités, processeurs DSP et autres approches, historique et évolutions récentes

Chapitre 2 : Arithmétique à virgule fixe et à virgule flottante (2 semaines )

- Numérisation des signaux, échantillonnage d’un signal analogique, quantification uniforme (caractéristique, caractéristique de l’erreur, dynamique ), quantification non-uniforme, quantification logarithmique (loi de compression expansion, approximations par segments des lois de compression A et µ), formats de représentations des nombres, codage des nombres entiers (entiers positifs ou non signés, complément à 1, complément à 2), représentation des nombres réels dans un calculateur (virgule fixe, virgule flottante)

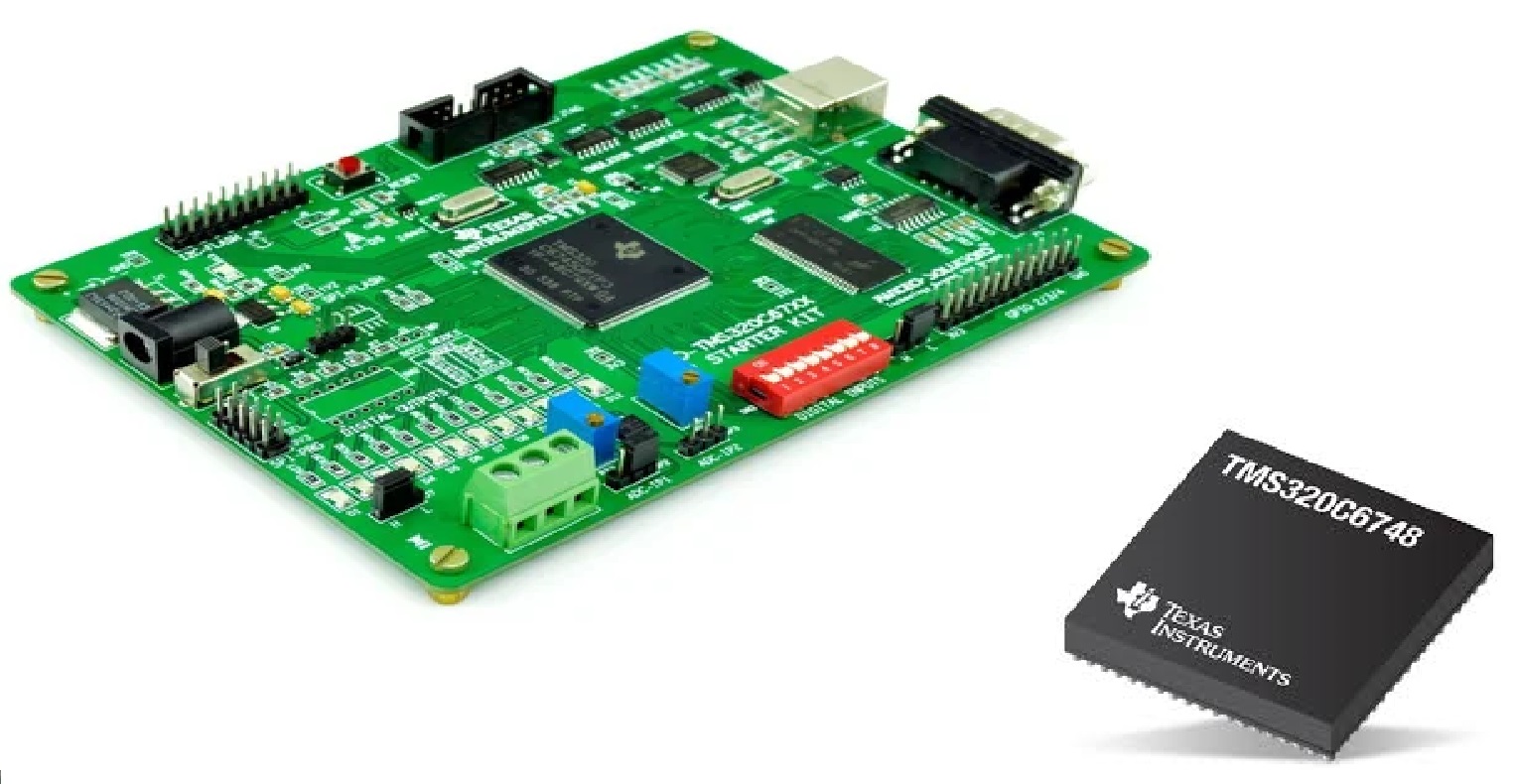

Chapitre 3 : Architecture des DSP TMS320C6x (4 semaines)

- Architecture interne du C6000, le processeur, cartographie de mémoire, unités fonctionnelles, paquets d’exécution et de fetch, architecture pipeline, les registres, les registres de contrôle, les périphériques (timers, PLL, interruptions, HPI, GPIO ), la liaison série (multichannel buffered serial port), présentation du jeu d'instructions

Chapitre 4 : Gestion de la mémoire (2 semaines )

- Présentation et intérêt de l'architecture Harvard. Mémoires internes (niveaux L1 et L2). Mémoires externes (SRAM, Flash, DDRAM, ...) Plan d'adressage des mémoires. Fichier *.cmd (organisation des sections).

- Gestion de la mémoire externe par L'EMIF (External Memory InterFace).

- Modes d'adressage (indirect, circulaire). Technique de transfert par blocs. Organisation des données pour l'EDMA.

- Paramètres et options pour l'EDMA. Exemple de transfert de données.

-

Chapitre 5 : Environnement de développement : ‘Code Composer Studio’ (CCS) (2semaines)

- Introduction, configuration de base ‘Basic Setup’, création d’un nouveau projet sous CCS, exécution du programme (Break Point, Watch Window, Plots, Images, enregistrement de données), scriptes GEL (General Extension Language) du CCS, utilisation des switches DIP et des LEDs

Chapitre 6 : Algorithmes de traitement du signal sur DSP (4 semaines)

- L'adéquation algorithme-architecture. Filtrage RIF et RII. Buffers à décalage et circulaire, problèmes de quantification, contraintes temps-réel, gestion des entrées/sorties. Implémentation de la FFT sur DSP (Adressage inversé).